Preston’s Law rules – predicting lapping and polishing performance

24th March 2015

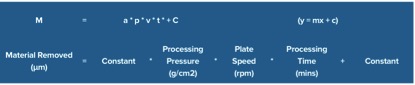

Preston’s Law enables the prediction of lapping and polishing rates and using it to model system performance can help improve processing efficiency and performance.

During the manufacture of semiconductor wafers, a number of physical processing steps are typically undertaken.

After slicing the wafer from the crystal and after lithographic processes, chemical-mechanical polishing (CMP) processes are employed to thin and finish the wafer surfaces.

The material removal rate (MRR) of CMP processes can be modelled using Preston’s Law which dictates that the polishing rate and accuracy are affected by the flow and composition of the slurry, the characteristics of the polishing plate, as well as the plate speed and processing pressure.

While lapping and polishing processes have become more predictable, there is often significant variation in the results obtained by different operators. Such variation can cause problems during the development and scale up of new devices.

Stringent quality requirements dictate that variations in the total thickness of the wafer, roughness of the surface and sample flatness must be minimised. This becomes even more important when processes are moved from the development stage to pilot and mass production stages.

Automated systems can remove this variability and help increase productivity during the development phase, and can also facilitate smoother transitions from development to production.

To learn more download our whitepaper.